Subscribe to Pittwire Today

Get the most interesting and important stories from the University of Pittsburgh.Engineering team studies new architecture for customized space computing

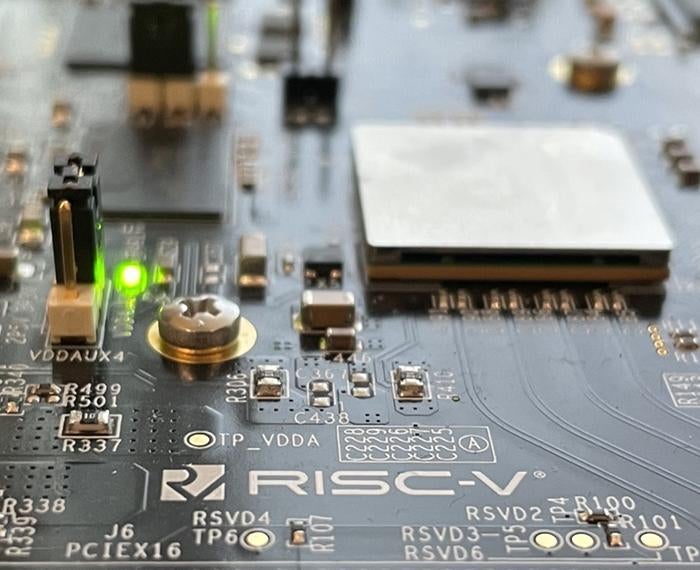

When choosing a processor for space computing, there are many factors that come into play: because of the rigors of a harsh environment, developers must find the optimal balance between size, weight, power and cost. An important variable in this design is the processor architecture, which can have a significant impact on balancing performance and power consumption.

Students at Pitt’s NSF Center for Space, High-performance and Resilient Computing (SHREC) examined the RISC-V architecture for space computing and received the Best Paper Award for Research in Space Computing at the 2021 IEEE Space Computing Conference.

Reduced Instruction Set Computer (RISC) is a more efficient approach to computing that uses a simple, optimized set of instructions compared to other architectures. RISC-V, in particular, is lauded for its modularity — a unique characteristic that sets it apart from other designs and allows users to add specialized functionality to individual systems.

According to the SHREC team, RISC-V may be particularly appealing for space missions.

“The architecture’s modularity means that different implementations of RISC-V can be used in a variety of space systems — from navigation and image processing to communications and machine learning,” said Evan Gretok, an electrical and computer engineering PhD student at Pitt.

Visit the Swanson School of Engineering website to learn more.